# Adiabatic Power Conversion (APOL) Technology Flight Insertion Status

March 20, 2019

Dong Tan, Henry Kuo, Tim Hsia and Henrik Gevorkyan

Approved for public release; NG 17-2595 dated 2/8/18.

THE VALUE OF PERFORMANCE.

NORTHROP GRUMMAN

Outline

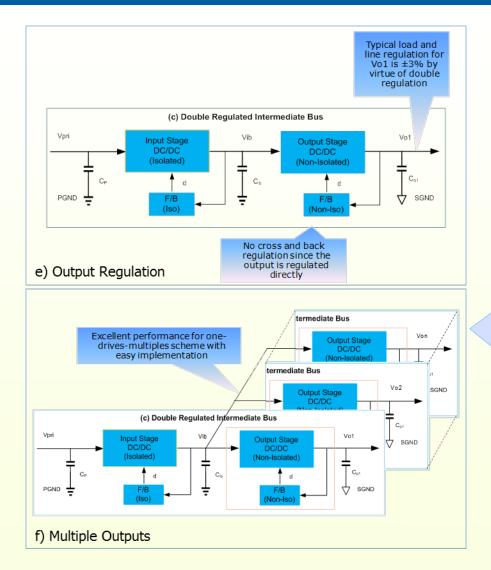

1. Double Regulated Intermediate Bus Architecture

#### 2. Bus Converter Modules

# 3. Point-of-Load Converters

Approved for public release; NG 17-2595 dated 2/8/18.

# **APOL Technology**

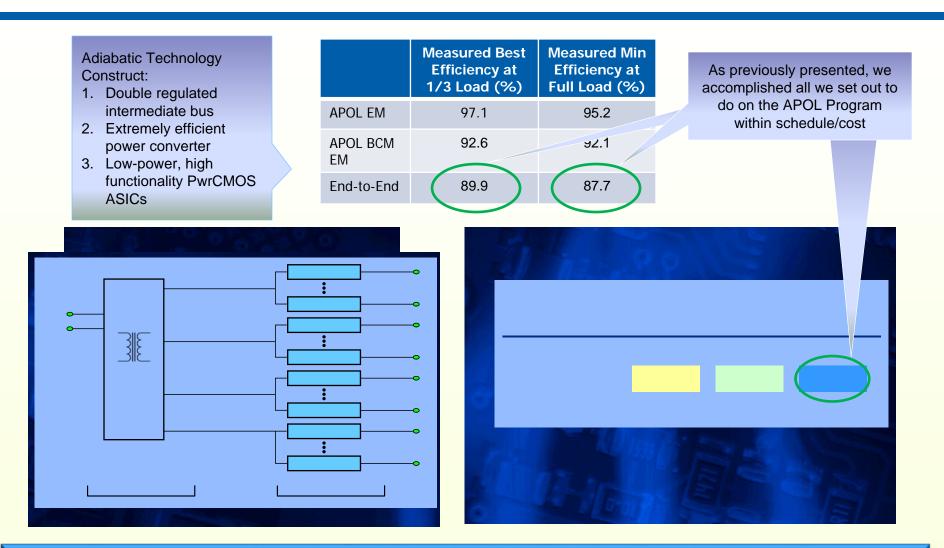

# Adiabatic Power Conversion Accomplishment

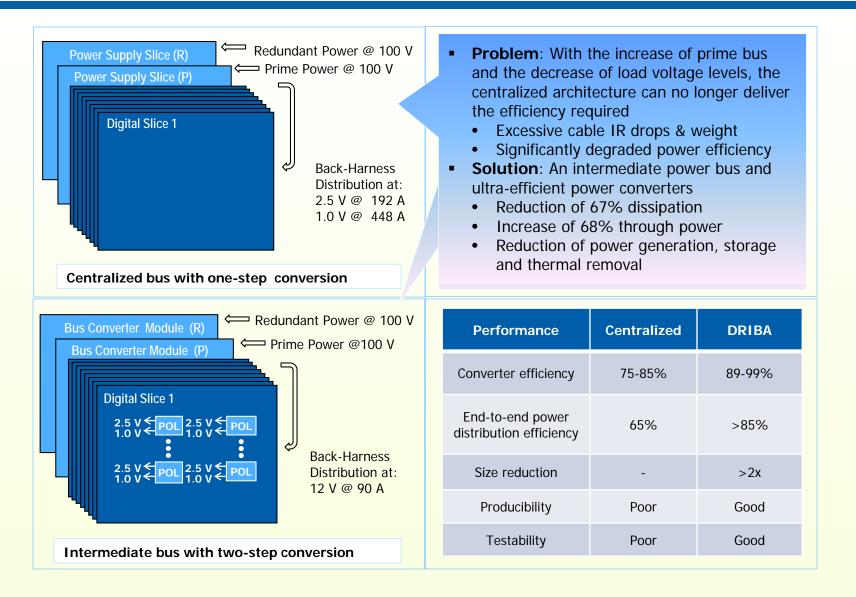

Double Regulated Intermediate Bus Architecture (DRIBA) Provides a Discriminating Technology Construct for Adiabatic Power Conversion, particularly for High Power/Low Voltage THE VALUE OF PERFORMANCE.

NORTHROP GRUMMAN

1. Double Regulated Intermediate Bus Architecture

# **DRIBA Key Advantages**

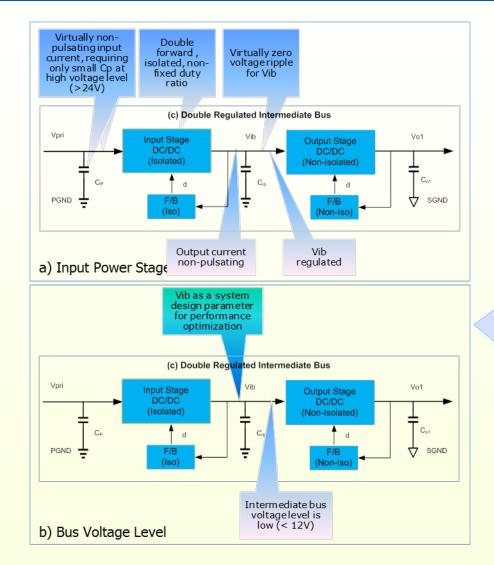

A significant departure from prior approaches is the ability to use the intermediate bus voltage to optimize at the system level

# DRIBA Key Advantages (cont'd)

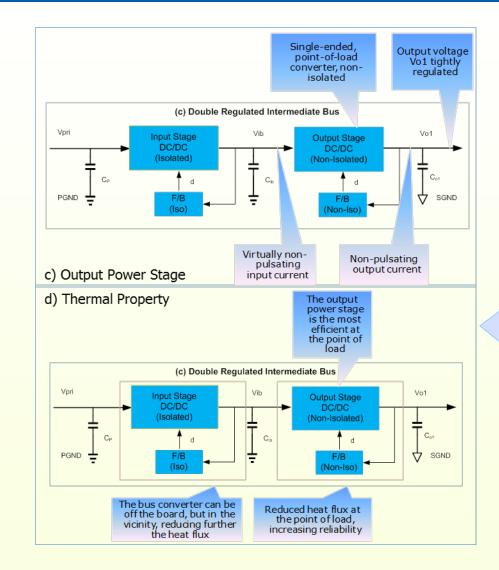

Virtually non-pulsating current at the intermediate bus and at the output

# DRIBA Key Advantages (cont'd)

Easy paralleling for multiple outputs with tight regulation

NORTHROP GRUMMAN

# **Comparison of Various Architectures**

|                     | Input Power<br>Stage                                                                                                                                                                                                              | Intermediat<br>e Bus<br>Voltage<br>Level                                                                                          | Output Power<br>Stage                                                                                                                                                                                          | Thermal<br>Property                                                                                                                                        | Regulation                                                                                                                                                 | Multiple<br>Outputs                  | System<br>Stability<br>& Output<br>Impedanc<br>e                                              |

|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|-----------------------------------------------------------------------------------------------|

| Regulated           | <ul> <li>Single ended, Buck<br/>or Buck-Boost,</li> <li>Pulsating input<br/>current with large<br/>cap at bus voltage<br/>level (usually &gt;24<br/>V)</li> <li>Output current can<br/>be pulsating</li> <li>Regulated</li> </ul> | High, usually ><br>12V                                                                                                            | <ul> <li>Double ended,<br/>push-pull, half<br/>or full bridge</li> <li>Virtually non-<br/>pulsating input<br/>current</li> <li>Virtually non-<br/>pulsating<br/>output current</li> <li>Unregulated</li> </ul> | <ul> <li>Most efficient<br/>power stage<br/>not at output</li> <li>Increase of<br/>point-of-load<br/>heat flux</li> <li>Reduced<br/>reliability</li> </ul> | <ul> <li>Typical<br/>load/line<br/>regulation<br/>&lt;±10%</li> <li>Cross<br/>regulation is<br/>large</li> <li>Back<br/>regulation is<br/>large</li> </ul> | • Poor,<br>>±10%,<br>typical         | <ul> <li>Favorable<br/>in stability</li> <li>Output<br/>impedanc<br/>e high</li> </ul>        |

| Unregulated         | <ul> <li>Double ended, half<br/>or full bridge as<br/>bus converter</li> <li>Virtually non-<br/>pulsating input<br/>current</li> <li>Non-pulsating<br/>output current</li> <li>Unregulated with<br/>fixed duty ratio</li> </ul>   | Low, usually <<br>12V                                                                                                             | <ul> <li>Single ended<br/>point of load<br/>(POL)</li> <li>Pulsating input<br/>current</li> <li>Non-pulsating<br/>output current</li> <li>Regulated</li> </ul>                                                 | <ul> <li>Most efficient<br/>power stage at<br/>the output</li> <li>Reduced point-<br/>of-load heat<br/>flux</li> <li>Increased<br/>reliability</li> </ul>  | <ul> <li>Typical<br/>load/line<br/>regulation<br/>&lt;±7%</li> <li>No cross<br/>regulation</li> <li>No back<br/>regulation</li> </ul>                      | • Good,<br>±5 -7<br>%,<br>typical    | <ul> <li>Not<br/>favorable<br/>in stability</li> <li>Output<br/>impedanc<br/>e low</li> </ul> |

| Double<br>Regulated | <ul> <li>Hybrid</li> <li>Virtually non-pulsating input current</li> <li>Non-pulsating output current</li> <li>Virtually zero voltage ripple</li> <li>Output regulated</li> </ul>                                                  | <ul> <li>Low, usually<br/>&lt; 12V</li> <li>Value as a<br/>design<br/>parameter<br/>for max<br/>system<br/>performance</li> </ul> | <ul> <li>Hybrid</li> <li>Virtually non-pulsating input current</li> <li>Non-pulsating output current</li> <li>Output current</li> <li>Output regulated</li> </ul>                                              | <ul> <li>Most efficient<br/>power stage at<br/>the output</li> <li>Reduced point-<br/>of-load heat<br/>flux</li> <li>Increased<br/>reliability</li> </ul>  | <ul> <li>Typical<br/>load/line<br/>regulation<br/>&lt;±3%</li> <li>No cross<br/>regulation</li> <li>No back<br/>regulation</li> </ul>                      | • Excellen<br>t,<br><±5%,<br>typical | <ul> <li>Favorable<br/>in stability</li> <li>Output<br/>impedanc<br/>e low</li> </ul>         |

\* - D. Tan, "A review of intermediate bus architecture: a system perspective," IEEE Journal of Emerging and Selected Topics inn Power Electronics, Vol. 2, No. 3, Sep., 2014, PP. 363-373

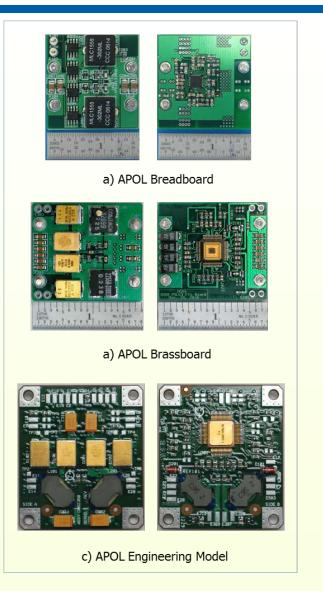

# **APOL Generic EM Hardware**

b) BCM Engineering Model

THE VALUE OF PERFORMANCE.

NORTHROP GRUMMAN

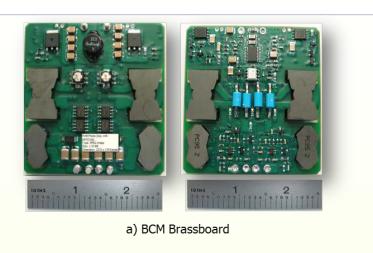

#### 2. Flight Insertion: BUS (Isolated) Converter Modules

# **Isolated Converters: ECA**

Key Features:

- Single-board assembly for superior manufacturability and testability

- Fully embedded planar magnetics

- Dedicated

PwrCMOS ASICs

- High EMI performance

- High efficiency

- Fully redundant design

| Parameters     | Performance      |

|----------------|------------------|

| Vin (V)        | 27 - 34          |

| Vo             | 6.3V at 4x16=84A |

| Size (in3)     | 7.8x8.0x11.0     |

| Efficiency (%) | 86               |

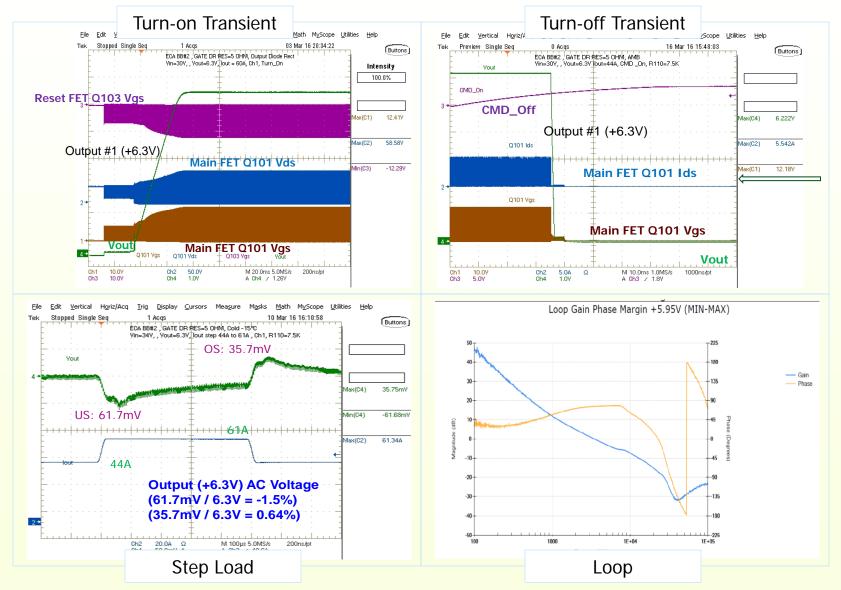

### **Isolated Converters: ECA Performance**

# **Isolated Converters: EDU**

Key Features:

- Single-board assembly for superior manufacturability and testability

- Fully embedded planar magnetics

- Dedicated PwrCMOS ASICs

- High EMI performance

- High efficiency

- Fully redundant design

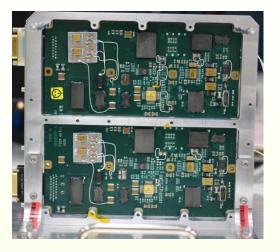

EDU FM

| Parameters     | Performance    |

|----------------|----------------|

| Vin (V)        | 27 - 34        |

| Vo             | 5.3V at 4.6A   |

|                | -5.1V at 0.19A |

| Size (in3)     |                |

| Efficiency (%) | 83             |

### **Isolated Converters: EDU Performance**

THE VALUE OF PERFORMANCE.

NORTHROP GRUMMAN

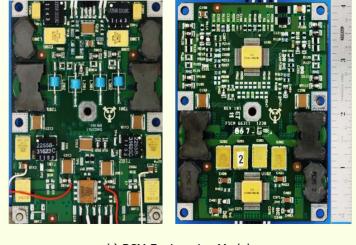

#### 3. Flight Insertion: Point-of-Load Converters

# Point-of-Load Converters: POL-A

| Parameters     | Performance     |

|----------------|-----------------|

| Input          | 4.9 – 5.2 V     |

| Output(s)      | 3.3V at 1.15A   |

|                | 1.82V at 0.82A  |

|                | -5.0V at 0.022A |

| Size (in3)     | 7.2x1.9x8.0     |

| Efficiency (%) | 83              |

#### POL-A Flight

#### Key Features:

- Single-board assembly for superior manufacturability and testability

- Fully embedded planar magnetics

- Dedicated PwrCMOS ASICs

- High EMI performance

- High efficiency

- Fully redundant design

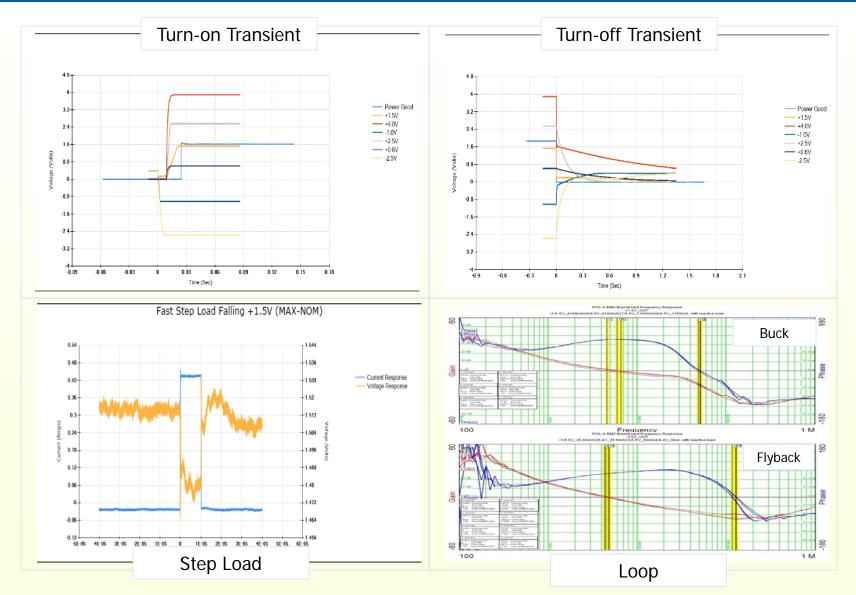

#### POL-A EM

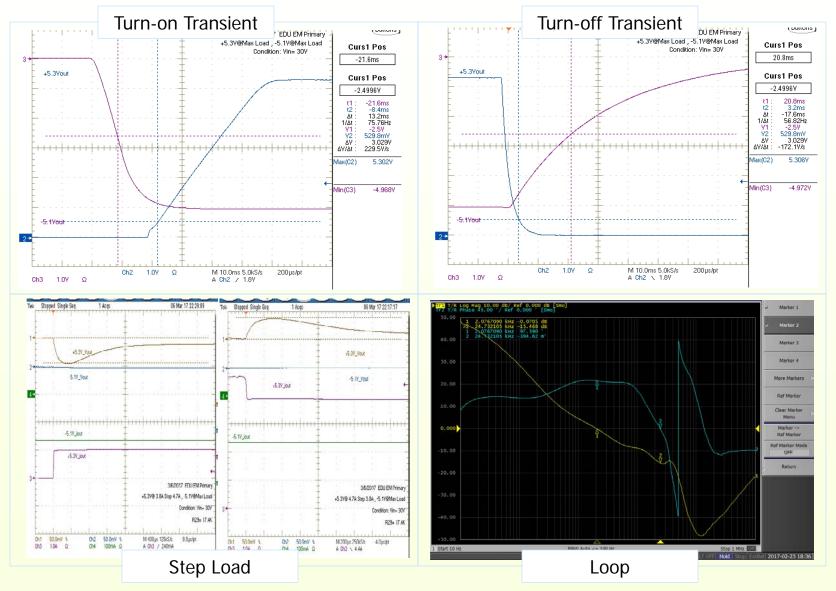

#### Point-of-Load Converters: POL-A Performance

Approved for public release; NG 17-2595 dated 2/8/18.

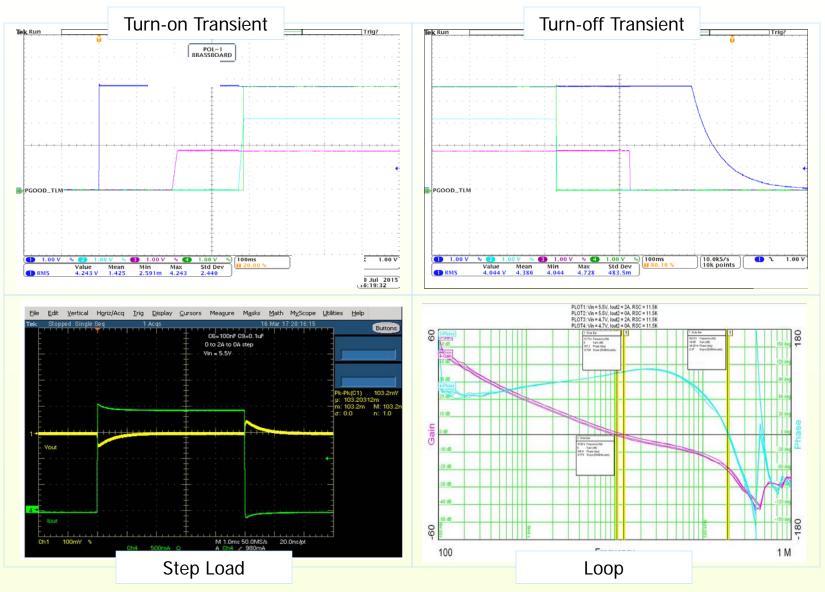

# Point-of-Load Converters: POL-1

#### Key Features:

- Single-board assembly for superior manufacturability and testability

- Fully embedded planar magnetics

- Dedicated PwrCMOS ASICs

- High EMI performance

- High efficiency

- Fully redundant design

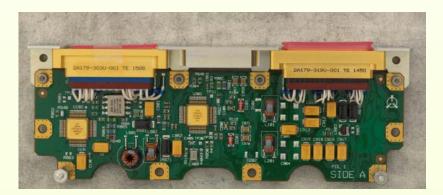

POL-1 Flight

| Parameters     | Performance       |

|----------------|-------------------|

| Input          | 4.9 – 5.2 V       |

| Output(s)      | 3.3V at 1.15A     |

|                | 1.82V at 0.82A    |

|                | -5.0V at 0.022A   |

| Size (in3)     | 2.47 x 0.5 x 6.68 |

| Efficiency (%) | 83                |

### Point-of-Load Converters: POL-1 Performance

Approved for public release; NG 17-2595 dated 2/8/18.

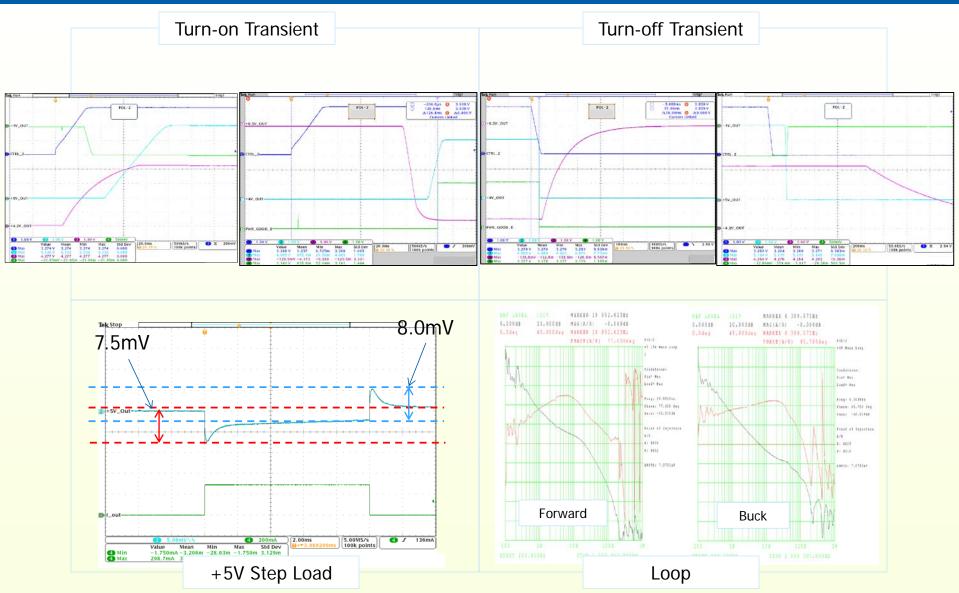

# Point-of-Load Converters: POL-2

| Parameters<br>Input<br>Output(s) | Performance           5.5 – 6.2 V           4.2V at 0.016A                                   | <ul> <li>Single-board assembly for superior<br/>manufacturability and testability</li> <li>Fully embedded planar magnetics</li> <li>Dedicated PwrCMOS ASICs</li> <li>High EMI performance</li> <li>High efficiency</li> <li>Fully redundant design</li> </ul> |

|----------------------------------|----------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Size (in3)                       | -1.0V at 0.246A<br>5.15V at 0.786A<br>6.5V at 0.025A<br>4.0V at 4.16A<br>20.45 x 4.265 x 1.8 |                                                                                                                                                                                                                                                               |

| Efficiency (%)                   | 86                                                                                           | POL-2 EM                                                                                                                                                                                                                                                      |

Approved for public release; NG 17-2595 dated 2/8/18.

### Point-of-Load Converters: POL-2 Performance

# THE VALUE OF PERFORMANCE.